Understanding Lattice Defects in Epitaxial Growth

Unlocking the secrets behind lattice defects can revolutionize the manufacturing process of semiconductors and other advanced materials.

The Fundamentals of Epitaxial Growth

Epitaxial growth is a process where a crystalline layer is grown on a crystalline substrate, ensuring that the new layer mirrors the underlying structure. This technique is of paramount importance in the manufacturing of semiconductors and other advanced materials, as it allows for the precise control of the material's properties at the atomic level. The alignment of the crystalline layers is critical, as it ensures that the electronic properties of the material are optimized for various applications, ranging from high-speed computing devices to efficient solar cells and advanced sensors.

Types of Lattice Defects: From Dislocations to Vacancies

Lattice defects are imperfections in the crystal structure that can significantly impact the material's properties, often leading to variations in performance and reliability. These defects can arise during the manufacturing process or as a result of external stresses and environmental conditions. The main types of lattice defects include dislocations, vacancies, and interstitials, each playing a unique role in altering the material's characteristics.

Dislocations are line defects where atoms are misaligned, causing a disruption in the crystal structure. This misalignment can create stress fields within the material, which may lead to a reduction in mechanical strength and an increase in the likelihood of failure under load. Dislocations can also impede the movement of electrons, thereby affecting the electrical conductivity and efficiency of semiconductor devices.

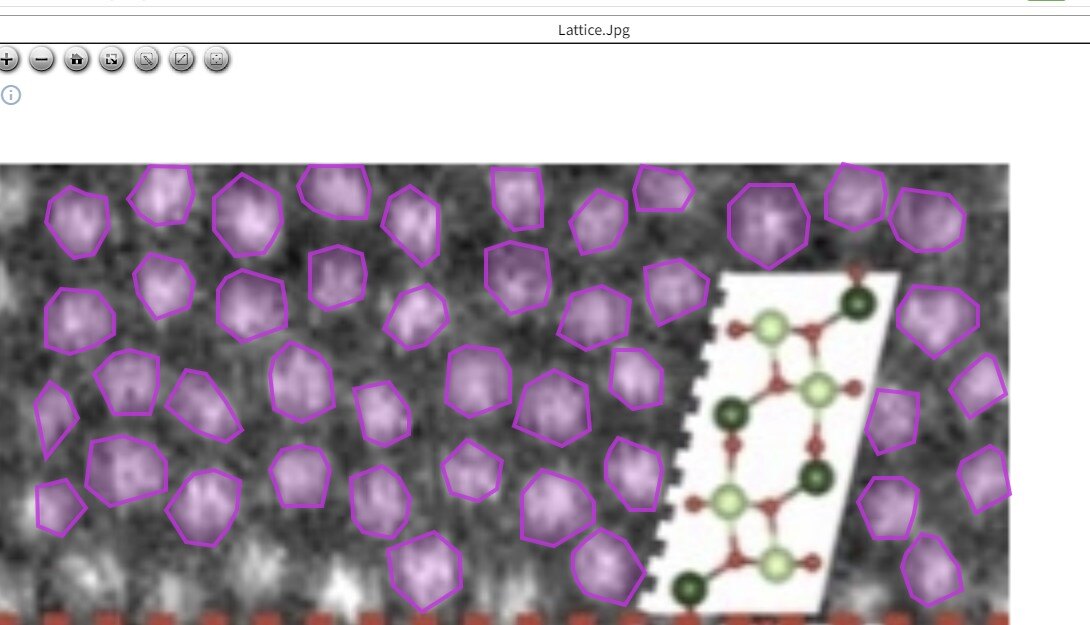

Using HR-TEM and STEM with DeepBlock.net for automatic alignment verification of Ga atoms

Vacancies occur when an atom is missing from its lattice site, creating a void that can alter the local electronic environment. This absence can lead to changes in the material's density and can affect properties such as thermal conductivity, as the missing atoms disrupt the regular flow of heat through the lattice. In electronic materials, vacancies can act as traps for charge carriers, reducing the mobility of electrons and holes and impacting the overall performance of the device.

Interstitials happen when extra atoms are inserted into the crystal lattice, often leading to distortions in the structure. These additional atoms can cause local expansions or contractions in the lattice, affecting the material's mechanical properties and potentially leading to increased brittleness or reduced ductility. Interstitials can also influence the electronic properties by introducing new energy levels within the band structure, which can modify the material's conductivity and optical characteristics.

Each type of defect affects the material differently, influencing factors like electron mobility, thermal conductivity, mechanical strength, and optical properties. Understanding and controlling these defects is crucial for optimizing the performance and reliability of advanced materials used in a wide range of applications, from high-speed electronics to energy-efficient solar cells and robust structural components.

Importance of Electron Mobility and Crystal Structure

Electron mobility is a key factor in determining the performance of semiconductor devices, as it directly influences the speed and efficiency with which these devices can operate. High electron mobility allows for faster electronic switching, which is essential for high-speed devices such as microprocessors, where rapid data processing and transmission are crucial. This characteristic is particularly important in applications that demand quick response times and high-frequency operations, such as telecommunications, computing, and advanced digital electronics.

The crystal structure of the material plays a significant role in electron mobility, as it dictates how easily electrons can traverse the material. A well-ordered crystal lattice with minimal defects ensures that electrons can move freely, enhancing the material's electronic properties by reducing scattering and resistance. This orderly arrangement allows for a smooth flow of electrons, which is vital for maintaining high performance in semiconductor devices. In contrast, any irregularities or disruptions in the crystal lattice can impede electron flow, leading to decreased efficiency and performance.

To increase electron mobility, it’s essential for the crystal lattice to be arranged in a regular pattern, as consistent atomic spacing improves this mobility by providing a uniform path for electron movement. This regularity minimizes the potential for scattering and energy loss, thereby optimizing the material's conductive properties. However, polycrystalline or amorphous structures, which lack this regular atomic arrangement, reduce electron mobility and can create electron traps. These traps are areas where electrons can become localized, disrupting the stable control of gate voltage and drain current. Such disruptions can lead to inefficiencies and instability in the operation of semiconductor devices, affecting their overall reliability and performance. Therefore, maintaining a well-ordered crystal structure is crucial for achieving high electron mobility and ensuring the optimal functionality of semiconductor components.

Epitaxial Layer and Lattice Constant of a Single Crystal Structure

A single crystal structure with a consistent lattice constant is essential for maintaining uniformity in the material's properties. This uniformity is crucial because any mismatch in the lattice constants can lead to the formation of defects, such as dislocations or vacancies, which can adversely impact the material's mechanical, thermal, and electronic performance. These defects can create stress fields, disrupt electron flow, and alter thermal conductivity, ultimately affecting the reliability and efficiency of the material in its intended applications.

The lattice constant is a fundamental parameter that refers to the distance, or bond spacing, between silicon atoms in the crystal lattice. This spacing is a key determinant of the material's structural integrity and performance. When other elements are introduced into the lattice, they can change the atomic charge and alter the atomic spacing, leading to potential variations in the lattice constant. Maintaining a consistent lattice constant is crucial because any variations can result in differences in thermal expansion, which can cause the wafer to warp or crack under thermal stress. This is particularly important in high-precision applications where even minor deviations can lead to significant performance issues.

To address these challenges, using an ultra-pure epitaxial layer, free from impurities, is vital for layers like gate oxides, such as silicon dioxide (SiO₂) or hafnium dioxide (HfO₂). These layers are critical in semiconductor devices, and their purity and structural integrity are paramount to preventing electron traps and misalignment at the interface. The unified lattice constant of an epitaxial layer helps minimize such issues, ensuring that the electronic properties of the material are optimized for high performance.

Despite the high quality of epitaxial layers, the process of creating them is complex and costly, which limits their use to specific applications where their benefits outweigh the challenges. The epitaxial growth process is inherently slow, as it requires the careful formation of a single crystal structure, layer by layer, to achieve the desired properties. This meticulous process demands precise control over the growth conditions and materials used, making it a specialized technique reserved for applications where the highest quality and performance are essential.

Lattice Match and Mismatch

Lattice match refers to the precise alignment of the crystal lattices of the epitaxial layer and the substrate, ensuring that the atomic arrangement of the two layers is perfectly synchronized. This alignment is crucial because a perfect lattice match minimizes the occurrence of defects, such as dislocations and vacancies, which can significantly impact the material's performance. When the lattice constants of the epitaxial layer and the substrate are identical, the resulting material exhibits enhanced mechanical, thermal, and electronic properties, making it ideal for high-performance applications in semiconductor devices and other advanced technologies.

Lattice mismatch, on the other hand, occurs when there is a discrepancy in the lattice constants of the epitaxial layer and the substrate. This mismatch can lead to the formation of various defects, including dislocations, voids, and hillocks, which degrade the material's properties and can compromise its structural integrity and functionality. The presence of these defects can result in stress fields within the material, affecting its mechanical strength and electronic performance. In semiconductor devices, such defects can impede electron mobility, leading to reduced efficiency and reliability.

When the lattice spacing of the Seed layer and the epitaxial layer match, it is known as homo-epitaxy (lattice match), where the epitaxial layer grows on a substrate of the same material, ensuring a seamless integration with minimal defects. In contrast, a mismatch is referred to as hetero-epitaxy (lattice mismatch), where the epitaxial layer is grown on a substrate of a different material. In hetero-epitaxy, if the epitaxial layer’s lattice spacing is larger than that of the Seed layer, compressive stress occurs as the layer attempts to align with the Seed layer. Conversely, if the lattice spacing is smaller, tensile stress arises, stretching the epitaxial layer to fit the Seed layer. Such mismatched lattices can lead to defects like voids or hillocks, which can significantly affect the quality and performance of the material.

To overcome these issues, a new epitaxial layer can be grown on the substrate to prevent dislocation or electron traps caused by mismatched lattice constants. This process involves carefully selecting materials with compatible lattice constants or employing buffer layers to gradually transition between different lattice structures. Additionally, doping during epitaxial growth allows the formation of layers with specific impurities, which can tailor the material's properties and make them suitable as substrates in semiconductor device fabrication. Doping can introduce controlled amounts of foreign atoms into the lattice, modifying its electronic properties and enhancing its performance for specific applications. By carefully managing these factors, manufacturers can produce high-quality materials with optimized properties for advanced technological applications.

Detection and Analysis Techniques: STEM and TEM

Scanning Transmission Electron Microscopy (STEM) and Transmission Electron Microscopy (TEM) are advanced and powerful techniques employed to detect and analyze lattice defects at the atomic level, providing invaluable insights into the structural integrity and composition of materials. STEM is particularly renowned for its ability to produce high-resolution images that reveal the intricate details of atomic arrangements. It also excels in analyzing the chemical composition of defects, allowing researchers to identify the specific elements and compounds present at defect sites. This capability is crucial for understanding how these defects form and how they might be mitigated or controlled in the manufacturing process.

On the other hand, TEM offers a complementary perspective by providing detailed insight into the crystal structure of materials. It allows scientists to visualize the arrangement of atoms within a crystal lattice, offering a clear view of any disruptions or irregularities that may exist. TEM is instrumental in examining the size, shape, and distribution of defects, such as dislocations, vacancies, and interstitials, within epitaxial layers. By combining the strengths of both STEM and TEM, researchers can gain a comprehensive understanding of the nature and distribution of defects in epitaxial layers, which is essential for optimizing the performance and reliability of advanced materials used in semiconductor devices and other high-tech applications. These techniques are indispensable tools in the ongoing quest to improve material quality and enhance the capabilities of modern technology.

Strategies to Minimize Lattice Defects in Manufacturing

An effective strategy involves the optimization of growth conditions, including parameters such as temperature, pressure, and deposition rate. These conditions are critical in promoting defect-free crystal growth, as they influence the rate at which atoms are deposited and incorporated into the growing crystal lattice. By fine-tuning these parameters, manufacturers can control the kinetics of the growth process, ensuring that atoms are arranged in a well-ordered manner and reducing the chances of defects forming. For instance, maintaining an optimal temperature can help in achieving a uniform deposition rate, which is essential for the formation of high-quality epitaxial layers with minimal defects.