Wafer Level Packaging: Key Processes and Benefits

Discover the key processes and benefits of wafer level packaging for efficient and high-performance semiconductor manufacturing in our comprehensive guide.

Understanding Wafer Level Packaging: An Overview

Wafer level packaging (WLP) is an advanced technology that involves the process of packaging an integrated circuit (IC) directly at the wafer level, as opposed to the conventional method of assembling and packaging each individual die separately. This approach allows for the production of semiconductor devices that are not only smaller and thinner but also more efficient in terms of performance and energy consumption.

The significance of WLP in the semiconductor industry cannot be overstated, as it plays a crucial role in enhancing the overall performance of electronic devices while simultaneously reducing manufacturing costs and minimizing space requirements.

Fan-In Wafer Level Chip Scale Packaging Process

Fan-In Wafer Level Chip Scale Packaging (WLCSP) is a specialized form of wafer level packaging where the input/output (I/O) pads are positioned within the die's footprint. This technique involves redistributing the pads to a wider pitch, followed by the application of solder bumps to establish electrical connections. This approach is particularly beneficial for applications that demand minimal package size and height, making it especially suitable for mobile and handheld devices. However, it is constrained by the limited number of I/O connections that can fit within the die's area.

In the Fan-In WLCSP process, once the wafer has completed testing and is introduced to the packaging line, a sputtering process is initially used to create a thin metal film layer. After sputtering, a thick layer of photoresist is applied, which must be thicker than the metal wiring intended for the package.

This photoresist is patterned using photolithography, and the exposed areas are electroplated with copper to form the metal wiring. After the wiring is established, the photoresist is stripped away, and any unnecessary metal film is removed through chemical etching. A dielectric layer is then formed on top, which is selectively removed in areas where solder balls will be placed, a process also known as solder resist (SR) application. This dielectric layer serves as the final protective layer of the WLCSP and restricts the areas where solder balls can attach.

Once the dielectric layer is patterned, the solder ball mounting process is carried out, attaching solder balls to the designated areas. Upon completion of the solder ball mounting, the packaging process is finalized, and the wafer is diced to produce individual Fan-In WLCSP units.

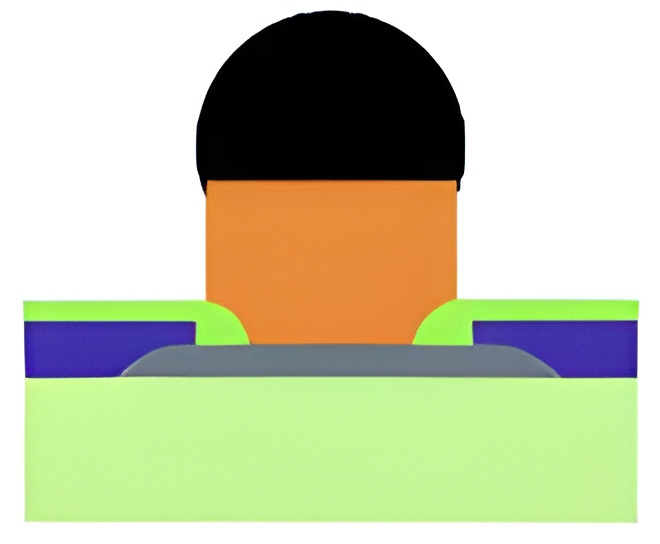

Flip Chip Bumping Process

The flip chip bumping process entails the formation of solder bumps on the input/output (I/O) pads of the wafer, which enables direct electrical connections to the substrate or printed circuit board (PCB). Once the solder bumps are created, the wafer is inverted to align these bumps with the corresponding pads on the substrate.

This technique offers numerous advantages, such as enhanced electrical performance, increased interconnect density, and superior thermal management. It is extensively utilized in high-performance computing and sophisticated electronics applications.

In this process, a photoresist is applied and patterned to accommodate the height of the bumps, using the thickest possible photoresist suitable for wafer level packaging.

Electroplating is then employed to form the solder bumps. For Copper Post Bump (CPB) or Copper Pillar Bump, copper is first plated, followed by a layer of solder, typically a lead-free Sn-Ag alloy. After plating, the photoresist is stripped away, and the thin film of Under Bump Metallurgy (UBM) created by sputtering is removed through metal etching.

Subsequently, wafer level reflow equipment is used to shape the bumps into spheres. This reflow process is crucial to minimize height differences between bumps, reduce bump roughness, and eliminate solder oxides, thereby enhancing the bonding quality during the flip chip bonding process.

Fan-Out Wafer Level Chip Scale Packaging Process

Fan-Out Wafer Level Chip Scale Packaging (FO-WLCSP) enhances the traditional WLCSP by enabling a greater number of input/output (I/O) connections that extend beyond the die's original dimensions. This is accomplished through a process that redistributes the I/O pads across a larger area using a reconstituted wafer technique.

FO-WLCSP is especially advantageous for applications that demand high I/O density, such as cutting-edge mobile processors and automotive electronics, as it provides superior electrical performance and reliability while maintaining a compact design.

The process of creating FO-WLCSP begins by attaching tape to a carrier shaped like a wafer. Chips that have passed quality testing are then placed at regular intervals on this carrier. Following this, wafer molding is employed to fill the spaces between the chips, forming a new wafer structure. Once the molding is complete, the carrier and tape are removed.

After that, metal wiring is created on the newly molded wafer using wafer equipment, and solder balls for packaging are attached.

The final step involves cutting the molded wafer into individual package units, thus completing the entire process.

Through-Silicon Via (TSV) Packaging Process

Through-Silicon Via (TSV) technology represents a 3D integration approach that facilitates the creation of vertical electrical pathways through a silicon wafer. This innovative method enables the stacking of multiple dies atop one another, thereby significantly enhancing the package's overall functionality and performance.

TSV packaging is particularly vital for applications that demand high bandwidth and low latency, such as those found in high-performance computing and data centers. Moreover, it supports the integration of diverse technologies by allowing different types of integrated circuits (ICs) to be combined within a single package.

The process begins with the formation of vias during the wafer processing stage. Solder bumps are then created on the wafer's front side, followed by the attachment of a carrier wafer. The wafer undergoes back grinding, and bumps are formed on the rear side before the wafer is diced into individual chips for stacking.

In the wafer process, TSV vias are typically formed using a via-middle approach. Initially, transistors like CMOS are established on the wafer (Front End of Line, FEOL). A pattern is created at the intended TSV locations using a Hard Mask (HM). The silicon is etched, removing areas without HM through a dry etching process to create deep trenches. An insulating layer, such as oxide, is deposited using Chemical Vapor Deposition (CVD) to prevent contamination from metals like copper (Cu) that will fill the trenches. A thin metal layer (Seed/Barrier) is then applied, which facilitates the electroplating of metals like Cu. After electroplating, Chemical-Mechanical Polishing (CMP) is used to planarize the surface and remove excess Cu, ensuring it remains only within the trenches. The wafer process concludes with subsequent wiring steps (Back End of Line, BEOL).

When constructing chip-stacked packages using TSV, two main types can be created. The first type involves building a 3D chip stack with a substrate, while the second type involves developing a Known Good Stack Die (KGSD), which can be further advanced into 2.5D or 3D packages. Let's explore the 2.5D packaging technique.

The process starts with forming flip chip bumps on the front sides of both the base and core wafers. The base wafer needs a bump array that can attach to an interposer in a 2.5D package, while the core wafer forms bumps for stacking chips. After creating bumps on the front, the wafer is thinned, and additional bumps are formed on the back. Thinning the wafer can lead to warping, as seen in conventional package processes.

And then, the wafer's front, with bumps formed, is temporarily bonded to a carrier wafer, and the back is ground to thin the wafer. The thin wafer remains unwarped due to its attachment to the carrier wafer.

Since the carrier wafer is also wafer-shaped, it can be processed using wafer equipment. This setup allows for bump formation on the back of the thin wafer. Once bumps are formed on both sides of the core wafer, the carrier is removed, and the wafer is attached to a ring frame with tape, similar to conventional package processes, before sawing/dicing.

The base wafer stays attached to the carrier wafer while chips diced from the core wafer are removed and stacked on the base wafer. After stacking, wafer molding is applied to the base wafer, and the carrier wafer is removed. This results in a molded wafer with stacked core chips. The wafer is then ground to a target thickness suitable for 2.5D packages and diced into individual chips, completing the KGSD.

Benefits and Challenges of Wafer Level Packaging

Wafer level packaging (WLP) offers a multitude of advantages that make it an attractive choice for modern semiconductor manufacturing. One of the primary benefits is the significant reduction in package size and height, which is crucial for the development of compact electronic devices.

This miniaturization allows for more efficient use of space within electronic products, enabling the creation of smaller, lighter, and more portable devices without compromising on functionality. Additionally, WLP enhances electrical performance by shortening the distance that electrical signals must travel, which reduces signal delay and improves overall device speed.

However, despite these advantages, there are several challenges associated with wafer level packaging that must be addressed to fully realize its potential.

One of the main challenges is the complexity of the processes involved in WLP. The intricate steps required to package devices at the wafer level demand precise control and coordination, which can be difficult to achieve without advanced technology and expertise.

Additionally, the need for specialized equipment and materials can increase the initial investment and operational costs for manufacturers. This requirement for cutting-edge technology and materials can also lead to potential reliability issues, as any defects or inconsistencies in the process can affect the performance and durability of the final product.

To overcome these challenges, continuous innovation and collaboration within the semiconductor industry are essential. This includes developing new materials and techniques to enhance the reliability and efficiency of WLP processes, as well as fostering partnerships between manufacturers, researchers, and technology providers to share knowledge and resources. By addressing these challenges, the industry can ensure that wafer level packaging continues to evolve and meet the growing demands for high-performance, compact, and cost-effective semiconductor devices.